MSP430G2553系统时钟设置

MSP430G2553系统时钟设置

《MSP430G2553系统时钟设置》由会员分享,可在线阅读,更多相关《MSP430G2553系统时钟设置(15页珍藏版)》请在装配图网上搜索。

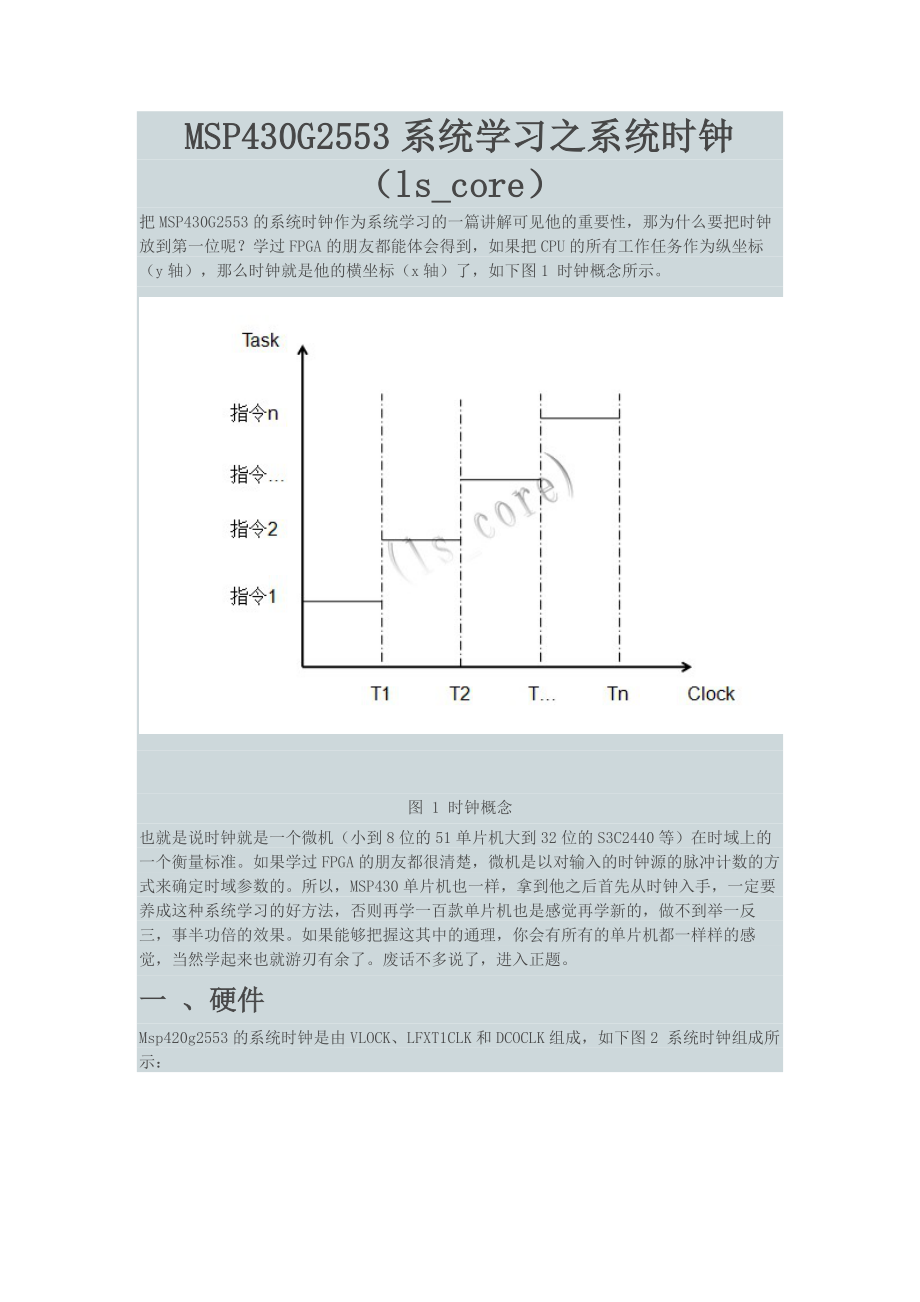

1、MSP430G2553系统学习之系统时钟(ls_core) 把MSP430G2553的系统时钟作为系统学习的一篇讲解可见他的重要性,那为什么要把时钟放到第一位呢?学过FPGA的朋友都能体会得到,如果把CPU的所有工作任务作为纵坐标(y轴),那么时钟就是他的横坐标(x轴)了,如下图1 时钟概念所示。 图 1 时钟概念 也就是说时钟就是一个微机(小到8位的51单片机大到32位的S3C2440等)在时域上的一个衡量标准。如果学过FPGA的朋友都很清楚,微机是以对输入的时钟源的脉冲计数的方式来确定时域参数的。所以,MSP430单片机也一样,拿到他之后首先从时钟入手,一定要养成这种系统学习

2、的好方法,否则再学一百款单片机也是感觉再学新的,做不到举一反三,事半功倍的效果。如果能够把握这其中的通理,你会有所有的单片机都一样样的感觉,当然学起来也就游刃有余了。废话不多说了,进入正题。 一 、硬件 Msp420g2553的系统时钟是由VLOCK、LFXT1CLK和DCOCLK组成,如下图2 系统时钟组成所示: 图2 系统时钟组成 即2553的系统时钟源有三个分别是片内超低功耗12KHz的内部振荡器;由外部时钟源提供的LFXT1CLK时钟源,也即LanuchPad开发板上未焊接的时钟电路,在这里我们可以焊接一个32.768KHz的低频时钟晶体由2553的XIN引脚输入;片内

3、可数字控制的振荡器DCOCLK,在软件的调节下该时钟的输出范围为0.6MHz到26MHz。在这三个时钟源的独立工作或是在三个时钟源相互协调配合(是可以通过软件配置的)下为2553系统提供了系统时钟ACLK、MCLK和SMCLK。 ACLK为辅助时钟,由软件选择来自VLOCK、LFXT1CLK之一经过1,2,4,8分频之后得到,为外围模块提供时钟源。 MCLK为主时钟,由软件选择来自VLOCK、LFXT1CLK和DCOCLK之一经过1,2,4,8分频之后得到,为CPU和系统提供时钟。 SMCLK为子系统时钟,由软件选择来自VLOCK、LFXT1CLK和DCOCLK之一经过1,2,4,8分频

4、之后得到,为外围各个模块提供时钟。 只有灵活掌握了系统时钟的配置之后才能为之后深入学习2553打下扎实的基础,例如之后再调试通用串口通信接口USCI时就不必考虑、担心自己的时钟是否配置错误的问题了,也为调试扫清了道路。 二、软件 了解了硬件构成便可以着手动手编写代码,对msp430g2553的系统时钟进行配置了,该代码的作用就是要实现对ACLK、MCLK和SMCLK的配置以供其他模块儿方便的使用。软件代码的编写笔者采用了模块儿化编程,这也是笔者在学习ARM(S3C2440)的时候体会到的一种对单片机应用的编程方法,今天就把这种布局应用于430单片机的应用之中。 / **********

5、********************************************************************************* * File name : clock.c * Creating time : 2012-7-11 * Author : 李帅 * pen-name : 亦然 * Organization : 济南大学 * Function : 该文件可用作模块儿化编程作为MSP430G2553的系统时钟配置文 件,在

6、工程的主函数中直接调用Init_Clk()函数即可对系统时钟

进行配置。

* Declareing : 如有错误的地方请各位指出,交流。交流使我们共同进步!

* Contact way : QQ:1021480125 博客lscore

**********************************************************************************************/

#include

7、 / *DCOCTL 寄存器*/ / ******************************************************************************** * bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 * DCO.2 CCO.1 DCO.0 MOD.4 MOD.3 MOD.2 MOD.1 MOD.0 * DCO.0——DCO.2定义8种频率之一,可分段调节DCOCLK频

8、率,相邻两种频率相差10%。 * 而频率由注入直流发生器的电流定义。 * MOD.O——MOD.4定义在32个DCO周期中插入的fdco+l周期个数,而在余下的DCO周期 * 中为fDco周期,控制切换DCO和DCO+1选择的两种频率。如果DCO常数为7,表示已 * 经选择最高颂率,此时不能利用进行频率调整。 * ********************************************************************************/ / *BCS

9、CTL1 寄存器*/ / ********************************************************************************** * bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 * XT2OFF XTS DIVA.1 DIVA.0 XT5V Rse1.2 Rse1.1 Rse1.0 *XT2OFF控制 XT2 振荡器的开启与关闭。 *XT2OFF=0,XT2振

10、荡器开启; *XT2OFF=1,XT2振疡器关闭(默认XT2关闭)。 *XTS控制 LFXTl 工作模武,选择需结合实际晶体振荡器连接情况。 *XTS=0,LFXTl工作在低频模式 (默认低频模式); *XTS=1,LFXTl工作在高频模式(必须连接有相应高频时钟源)。 *DIVA.0,DIVA.l控制ACLK分频。 *0 不分频(默认不分频); *1 2分频; *2 4分频; *3 8分频。 *XT5V此位设置为0。 *Rse1.0,Rsel.l,Rse1.2三位控制某个内部

11、电阻以决定标称频率。 *Rse1=0,选择最低的频率; *Rse1=7,选择最低的标称频率; ***********************************************************************************/ / *BCSCTL2 寄存器*/ / *********************************************************************************** * bit7

12、 bit6 bit5 bit4 bit3 bit2 bit1 bit0 *SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR *SELM.1,SELM.0选择 MCLK 时钟源。 *0 时钟源为 DCOLCK(默认时钟源); *1 时钟源为DCOCLK ; *2 时钟源为LFXTlCLK; *3 时钟源为 LFXT1CLK 。 *DIVM.1,DlVM.0选择 MCLK 分频。

13、 *0 1分频(默认MCLK=DCOCLK); *1 2分频; *2 4分频; *3 8分频。 *DIVS.1,DIVS.0选择 SMCLK 分频。 *0 1分频(默认 SMCLK=MCLK); *1 2分频; *2 4分频; *3 8分频。 ************************************************************************************/ / *B

14、CSCTL3 寄存器*/ / ************************************************************************************ * bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 * XT2S1 XT2S0 LFXT1S1 LFXT1S0 XCAP1 XCAP0 XT2OF LFXT1OF * XT2S1和XT2S0(2553不支持) * LFXT1S1和LF

15、XT1S0选择LFXT1的范围。 * XCAP1和XCAP0选择LFXT1的匹配电容 * 00 1pf * 01 6pf * 10 10pf * 11 12.5pf ************************************************************************************/ / *************************************************************************************

16、*** * 静态函数声明 ********************************************************************/ static void DcoClkSet(unsigned char x,unsigned char y); //msp430g2553datasheet P30 static void MClkSet(unsigned char Div); static void SMClkSet(unsigned char Div); static void AClkSet(unsigned char Div); / *

17、*********************************************************************** * 函数名 : DcoClkSet * 函数功能 : 对时钟DCOCLK进行配置 * 函数形参 : 传入的形参为x和y,其值参考2553datsheet第28页中DCO频率表 * 函数返回值 : 无 ************************************************************************/ void DcoClkSet(unsigned char x,un

18、signed char y) // msp430g2553datasheet P30 { DCOCTL &=~( 0xFF); BCSCTL1 &=~( 0xFF); unsigned char temp=(x<<4)+y; switch(temp){ case 0x00: { DCOCTL &=~( DCO0 + DCO1 + DCO2); BCSCTL1 &=~( RSEL0 + RSEL1 + RSEL2 + RSEL3); break;

19、} case 0x03: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 &=~( RSEL0 + RSEL1 + RSEL2 + RSEL3); break; } case 0x13: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL0 ); break; } case 0x23: {

20、 DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL1 ); break; } case 0x33: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL0 + RSEL1 ); break; } case 0x43: { DCOCTL |= ( DCO0 + DCO1 );

21、 BCSCTL1 |= ( RSEL2); break; } case 0x53: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL0 + RSEL2 ); break; } case 0x63: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL1 + RSEL2 );

22、 break; } case 0x73: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL0 + RSEL1 + RSEL2 ); break; } case 0x83: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL3); break; } case 0

23、x93: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL0+ RSEL3); break; } case 0xA3: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL1 + RSEL3); break; } case 0xB3: { DCOCTL |= ( DCO0

24、+ DCO1 ); BCSCTL1 |= ( RSEL0 + RSEL1 + RSEL3); break; } case 0xC3: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL2 + RSEL3); break; } case 0xD3: { DCOCTL |= ( DCO0 + DCO1 ); DCOCTL

25、|= ( MOD4 + MOD3 + MOD2 + MOD1 + MOD0 );//微调DCOCLK BCSCTL1 |= ( RSEL0 + RSEL2 + RSEL3); break; } case 0xE3: { DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL1 + RSEL2 + RSEL3); break; } case 0xF3: {

26、 DCOCTL |= ( DCO0 + DCO1 ); BCSCTL1 |= ( RSEL0 + RSEL1 + RSEL2 + RSEL3); break; } case 0xF7: { DCOCTL |= ( DCO0 + DCO1 + DCO2 ); BCSCTL1 |= ( RSEL0 + RSEL1 + RSEL2 + RSEL3); break; } default: {

27、 DCOCTL |= ( DCO0 + DCO1 + DCO2 ); BCSCTL1 |= ( RSEL0 + RSEL1 + RSEL2 + RSEL3); } } } / ******************************************************************** * 函数名 : MClkSet * 函数功能 : 对时钟MCLK进行配置 * 函数形参 : 传入的形参为Div,对时钟源DCOCLK进行Div分频 * 函数返回值 : 无 ************

28、********************************************************/ void MClkSet(unsigned char Div) { BCSCTL2 &= ~(SELM1+SELM0); //select DCOCLK for MCLK switch(Div){ //1分频 case 0x01:{ BCSCTL2 &=~(DIVM1 + DIVM0); break; }

29、 case 0x02:{ //2分频 BCSCTL2 &=~(DIVM1 + DIVM0); BCSCTL2 |=DIVM0; break; } case 0x04:{ //4分频 BCSCTL2 &=~(DIVM1 + DIVM0); BCSCTL2 |=DIVM1; break; }

30、case 0x08:{ //8分频 BCSCTL2 |=(DIVM1 + DIVM0); break; } default :{ //默认不分频 BCSCTL2 &=~(DIVM1 + DIVM0); } } } / ******************************************************************** * 函数

31、名 : SMClkSet * 函数功能 : 对时钟MCLK进行配置 * 函数形参 : 传入的形参为Div,对时钟源DCOCLK进行Div分频 * 函数返回值 : 无 ********************************************************************/ void SMClkSet(unsigned char Div) { BCSCTL2 &= ~(SELM1+SELM0); //select DCOCLK for SMCLK switch(Div){ c

32、ase 0x01:{ //1分频 BCSCTL2 &=~(DIVS_3); break; } case 0x02:{ //2分频 BCSCTL2 &=~(DIVS_3); BCSCTL2 |=(DIVS_1); break; } case 0x04:{ //4分频

33、 BCSCTL2 &=~(DIVS_3); BCSCTL2 |=(DIVS_2); break; } case 0x08:{ //8分频 BCSCTL2 |=(DIVS_3); break; } default :{ //默认不分频 BCSCTL2 &=~(DIVS_3); }

34、} } / ******************************************************************** * 函数名 : AClkSet * 函数功能 : 对时钟MCLK进行配置 * 函数形参 : 传入的形参为Div,对时钟源LFXT1CLK进行Div分频 * 函数返回值 : 无 ********************************************************************/ void AClkSet(unsigned char Div) { BCSCTL1

35、 &=~(XTS); //low-frequency mode switch(Div){ case 0x01:{ //1分频 BCSCTL1 &=~(DIVA_3); break; } case 0x02:{ //2分频 BCSCTL1 &=~(DIVA_3); BCSCTL1 |=(DIVA_1);

36、 break; } case 0x04:{ //4分频 BCSCTL1 &=~(DIVA_3); BCSCTL1 |=(DIVA_2); break; } case 0x08:{ //8分频 BCSCTL1 |=(DIVA_3); break; } default :{

37、 //默认不分频 BCSCTL1 &=~(DIVA_3); } } BCSCTL3 |= XT2S0 + LFXT1S0 + XCAP_3; //配置ACLK匹配电容 } / ******************************************************************** * 名称 : Init_Clk() * 功能 : MSP430时钟系统初始化程序 * 输入 : 无 * 返回值 : 无 **********

38、**********************************************************/ void Init_Clk() //时钟系统设置 { DcoClkSet(13,3); //7.84MHz 2553datasheet 第28页 AClkSet(0x08); //8分频LFXT1CLK SMClkSet(0x08); //8分频DCOCLK MClkSet(0x01); //8分

39、频DCOCLK

}

/ ************************ end of file *************************/

在编写好代码之后,为了验证是否正确,笔者在CCS4下面建立了一个工程,并在主函数中调用Init_Clk();

#include

40、k(); } 通过示波器看起输出波形是否正确。下图3 SMCLK波形中示波器所示波形为系统经过8分频DCOCLK后得到的SMCLK,其大小为0.98MHz正好是DcoClkSet(13,3)之后得到的DCOCLK时钟(7.84MHz)经过8分频之后的大小。 图 3 示波器观察SMCLK输出波形 好啦,讲了这些希望初学者对对系统时钟有一个整体把握,希望前辈能多多指正,谢谢!我在后面还会将我的学习心得整理成文,包括FPGA和ARM等。再次声明,文中若有技术错误或是不足望各位多多指正,多多交流。共同交流使得我们共同进步!希望将我的学习心得与您分享,谢谢!下次总结再见。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。