第15章时序逻辑电路3-寄存器课件

第15章时序逻辑电路3-寄存器课件

《第15章时序逻辑电路3-寄存器课件》由会员分享,可在线阅读,更多相关《第15章时序逻辑电路3-寄存器课件(46页珍藏版)》请在装配图网上搜索。

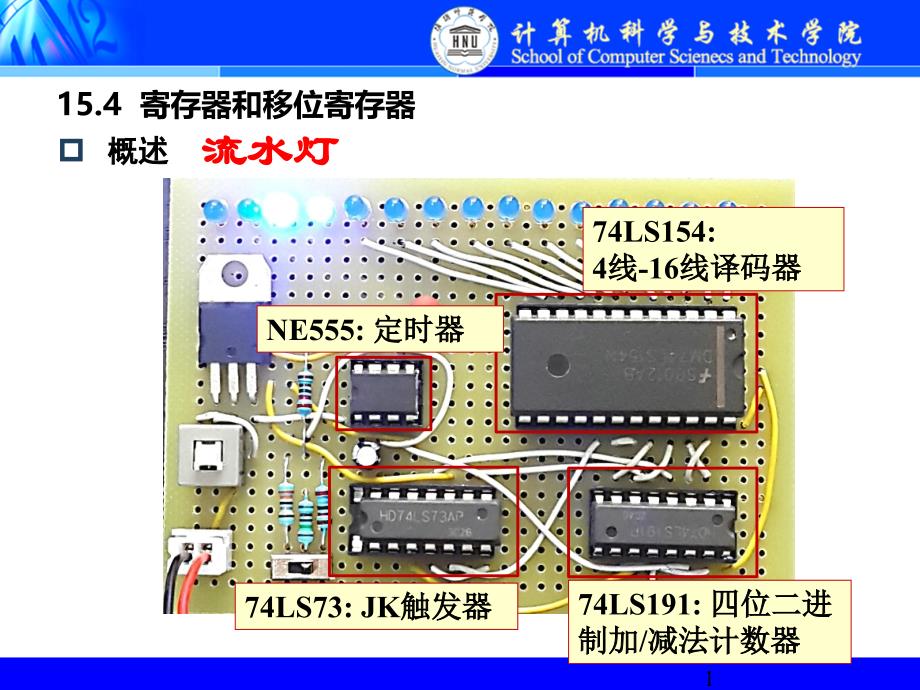

1、,*,*,*,*,*,*,*,*,*,*,*,*,*,*,*,15.4,寄存器和移位寄存器,概述,74LS191:,四位二进制加,/,减法计数器,74LS73:JK,触发器,74LS154:,4,线,-16,线译码器,NE555:,定时器,流水灯,15.4 寄存器和移位寄存器 概述74LS191:四位二,1,15.4,寄存器和移位寄存器,概述,15.4 寄存器和移位寄存器 概述,2,知识点回顾,15.4,寄存器和移位寄存器,输入信号,次态,Q,n,+1,D,0,1,1,0,0,D=,1,1,D=,1,D=,0,D=,0,D,触发器的特点:,只要向触发器送入一个,CP,,可将输入数据,D,存入触

2、发器,CP,过后,触发器将存储该数据,直到下一个,CP,到来时为止。,D,C,R,Q,Q,CP,Q,n,+1,=D,知识点回顾15.4 寄存器和移位寄存器输入信号次态Q n,3,寄存器的概念,寄存器,:寄存器是数字系统常用的逻辑部件,它用来存放数据或指令等。它由触发器和门电路组成。,功能,:,接收、存放和清除数码的功能。,构成,:,一个触发器可以存储,1,位二进制代码。,存放,n,位二进制代码的寄存器,需用,n,个触发器来构成,。,15.4,寄存器和移位寄存器,寄存器的概念寄存器:寄存器是数字系统常用的逻辑部件,它用来,4,寄存器的分类,基本寄存器,15.4,寄存器和移位寄存器,只能并行送入数

3、据,需要时也只能并行输出。,R,D,C,Q,0,D,0,R,D,C,Q,1,D,1,R,D,C,Q,2,D,2,R,D,C,Q,3,D,3,CP,寄存指令,R,D,清零,FF,0,FF,3,FF,2,FF,1,移位寄存器,数据可以在移位脉冲作用下依次逐位右移或左移。,寄存器的分类基本寄存器15.4 寄存器和移位寄存器只能并,5,寄存器的分类,根据,数据传输,方式,并行输入、并行输出,并行输入、串行输出,串行输入、串行输出,15.4,寄存器和移位寄存器,串行输入、并行输出,寄存器的分类根据数据传输方式并行输入、并行输出并行输入、串,6,单向移位寄存器,特点:,由,4,个上升沿触发的,D,触发器构

4、成;,各级触发器在同一时钟沿作用下翻转;,每级触发器输出端接到下一级的输入端,15.4,寄存器和移位寄存器,CP,D,C,R,Q,0,串行输入,D,R,D,D,C,R,Q,1,D,C,R,Q,2,D,C,R,Q,3,串行输出,FF,0,FF,1,FF,2,FF,3,并行输出,Q,n,+1,=,Q,n,1,0,Q,n,+1,=,D,0,Q,n,+1,=,Q,n,2,1,Q,n,+1,=,Q,n,3,2,1011,1,1,0,0,1,1,0,1,1,单向移位寄存器特点:15.4 寄存器和移位寄存器CPD,7,单向移位寄存器,15.4,寄存器和移位寄存器,并行输出,0,0 0 0 0,1,1,0 0

5、 0,1,0,2,0 0,1,0,1,3,0,1,0,1,1,4,1,0,1,1,1 0 1 1,D,CP,Q,3,Q,2,Q,1,Q,0,左移寄存器状态转移表,单向移位寄存器15.4 寄存器和移位寄存器并行输出00,8,单向移位寄存器,15.4,寄存器和移位寄存器,左移寄存器波形图,Q,0,Q,1,Q,2,1 2 3 4 5 6 7 8,CP,D,Q,3,单向移位寄存器15.4 寄存器和移位寄存器左移寄存器波形,9,单向移位寄存器,15.4,寄存器和移位寄存器,CP,D,C,R,Q,0,串行输入,D,R,D,D,C,R,Q,1,D,C,R,Q,2,D,C,R,Q,3,串行输出,FF,0,FF

6、,1,FF,2,FF,3,并行输出,单向移位寄存器15.4 寄存器和移位寄存器CPD CRQ,10,双向移位寄存器,15.4,寄存器和移位寄存器,R,C,D,Q,Q,&,CP,R,D,Q,0,R,C,D,Q,Q,&,Q,1,R,C,D,Q,Q,&,Q,2,R,C,D,Q,Q,&,Q,3,1,1,1,右移输入,左移输入,D,SR,控制,X,D,SL,X,=1,右移,;,X,=0,左移,X Q,n,Q,n,+1,=,X D,SR,0,1,+,X Q,n,Q,n,+1,=,X Q,n,2,3,+,1,X Q,n,Q,n,+1,=,X Q,n,1,2,+,0,X D,SL,Q,n,+1,=,X Q,n

7、,3,+,2,双向移位寄存器15.4 寄存器和移位寄存器R CDQQ&,11,双向移位寄存器,15.4,寄存器和移位寄存器,X Q,n,Q,n,+1,=,X D,SR,0,1,+,X Q,n,Q,n,+1,=,X Q,n,2,3,+,1,X Q,n,Q,n,+1,=,X Q,n,1,2,+,0,X D,SL,Q,n,+1,=,X Q,n,3,+,2,X,=1,Q,n,+1,=,D,SR,0,Q,n,+1,=,Q,n,2,Q,n,+1,=,Q,n,1,Q,n,+1,=,Q,n,3,1,0,2,X,=0,Q,n,+1,=,Q,n,0,Q,n,+1,=,Q,n,2,Q,n,+1,=,Q,n,1,Q,

8、n,+1,=,D,SL,3,3,2,1,数码右移,数码左移,双向移位寄存器15.4 寄存器和移位寄存器X Q n Q,12,中规模移位寄存器,15.4,寄存器和移位寄存器,D,C,R,Q,0,&,D,C,R,Q,1,D,C,R,Q,2,D,C,R,Q,3,&,&,&,&,1,1,1,CP,D,SR,S,1,S,0,D,0,D,1,D,2,D,3,D,SL,CR,中规模移位寄存器15.4 寄存器和移位寄存器D CRQ0,13,中规模移位寄存器,15.4,寄存器和移位寄存器,74LS 194,CR,D,SR,D,0,D,1,D,2,D,3,D,SL,GND,V,CC,Q,0,Q,1,Q,2,Q,3

9、,CP,S,1,S,0,CR,CP,D,SR,Q,0,Q,1,Q,3,Q,2,D,0,D,1,D,2,D,3,S,0,S,1,清零,右移串行输入,左移串行输入,并行输入端,输出端,控制信号,中规模移位寄存器15.4 寄存器和移位寄存器74LS 1,14,中规模移位寄存器,15.4,寄存器和移位寄存器,功能,清,零,CR,控制信号,串行输入,时钟,CP,并行输入,输 出,S,1,S,0,D,SR,D,SL,D,0,D,1,D,2,D,3,Q,0,Q,1,Q,2,Q,3,74LS194,功能表,清零,0,X X X X X X X X X,0 0,0 0,置数,1 1 1,X X,a,b c d,

10、a,b c d,右移,1 0 1,d,0,X,X X X X,d,0,Q,n,Q,n,Q,n,0,2,1,左移,1 1 0,X,d,0,X X X X,Q,n,Q,n,Q,n,d,0,1,3,2,保持,1 0 0,X X,X X X X X,Q,n,Q,n,Q,n,Q,n,0,2,1,3,中规模移位寄存器15.4 寄存器和移位寄存器功能清控制信,15,中规模移位寄存器,15.4,寄存器和移位寄存器,移位寄存器的,应用:,数据寄存(并入并出),多位数据共信道传输(并入串出),共信道传输数据接收,(串入并出),信号延迟(串入串出),中规模移位寄存器15.4 寄存器和移位寄存器移位寄存器的,16,中

11、规模移位寄存器,15.4,寄存器和移位寄存器,串行,-,并行转换,1,CR,CP,D,SR,Q,0,Q,1,Q,3,Q,2,D,0,D,1,D,2,D,3,S,0,S,1,Q,0,Q,1,Q,2,Q,3,CR,CP,D,SR,1,Q,0,Q,1,Q,2,Q,4,Q,5,Q,6,Q,3,D,0,D,1,D,2,D,3,S,1,S,0,CR,CP,0,1,1,串行输入,D,0,D,1,D,2,D,3,D,4,D,5,D,6,并行输出,中规模移位寄存器15.4 寄存器和移位寄存器串行-并行转,17,15.4,寄存器和移位寄存器,中规模移位寄存器,并行,-,串行转换,串行输出,CR,CP,D,SR,Q

12、,0,Q,1,Q,3,Q,2,D,0,D,1,D,2,D,3,S,0,S,1,1,CR,CP,D,SR,1,Q,0,Q,1,Q,2,Q,3,D,0,D,1,D,2,D,3,S,1,S,0,CP,0,D,0,D,1,D,4,D,5,并行输入,1,1,D,6,D,3,D,2,&,&,1,G,2,G,1,启动,15.4 寄存器和移位寄存器 中规模移位寄存器并行-串行转,18,概述,15.5,时序逻辑电路的设计,根据给定问题的逻辑要求来设计电路,力求使电路最简。,小规模集成电路设计时序电路:,触发器和逻辑门数最少;,输入端口数最少。,中规模集成电路设计时序电路:,集成电路的数目和种类最少;,相互间连线

13、最少。,概述15.5 时序逻辑电路的设计根据给定问题的逻辑要求来,19,同步时序电路设计步骤,15.5,时序逻辑电路的设计,分析设计要求,建立原始状态图、状态表,对逻辑问题的正确理解;,所有可能的情况都考虑进来,状态简化,同步时序电路设计步骤15.5 时序逻辑电路的设计分析设计,20,同步时序电路设计步骤,15.5,时序逻辑电路的设计,分析设计要求,建立原始状态图、状态表,状态简化,状态分配,状态表中的各个状态按一定的规律赋予二进制代码,即,状态编码,。,状态分配一般原则:,“次态相同,现态相邻”,“同一现态,次态相邻”,输出相同的状态代码相邻,同步时序电路设计步骤15.5 时序逻辑电路的设计

14、分析设计,21,同步时序电路设计步骤,15.5,时序逻辑电路的设计,分析设计要求,建立原始状态图、状态表,状态简化,状态分配,触发器选择,确定激励函数、输出函数,消除孤立状态,画出电路图,检查电路,能否自启,同步时序电路设计步骤15.5 时序逻辑电路的设计分析设计,22,15.5,时序逻辑电路的设计,例,15-2,设计一个串行数据检测器。要求连续输入,4,个或,4,个以上的,1,时,输出为,1,;否则,输出为,0,。,建立状态图、状态表,S,0,0,/,0,x,/,F,S,1,1,/,0,0,/,0,1,/,0,S,2,0,/,0,S,3,1,/,0,0,/,0,S,4,1,/,1,1,/,1

15、,0,/,0,S,0,0,/,0,x,/,F,S,1,1,/,0,0,/,0,1,/,0,S,2,0,/,0,S,3,1,/,1,1,/,1,0,/,0,15.5 时序逻辑电路的设计 例15-2 设计一个串行数据,23,15.5,时序逻辑电路的设计,例,15-2,设计一个串行数据检测器。要求连续输入,4,个或,4,个以上的,1,时,输出为,1,;否则,输出为,0,。,建立状态图、状态表,S,0,0,/,0,x,/,F,S,1,1,/,0,0,/,0,1,/,0,S,2,0,/,0,S,3,1,/,1,1,/,1,0,/,0,S,n,S,n,+1,0,1,简化状态表,/,F,x,S,0,S,1,

16、S,2,S,3,S,0,/,0,S,1,/,0,S,0,/,0,S,0,/,0,S,0,/,0,S,2,/,0,S,3,/,0,S,3,/,0,15.5 时序逻辑电路的设计 例15-2 设计一个串行数据,24,15.5,时序逻辑电路的设计,例,15-2,设计一个串行数据检测器。要求连续输入,4,个或,4,个以上的,1,时,输出为,1,;否则,输出为,0,。,状态分配,S,n,S,n,+1,0,1,简化状态表,/,F,x,S,0,S,1,S,2,S,3,S,0,/,0,S,1,/,0,S,0,/,0,S,0,/,0,S,0,/,0,S,2,/,0,S,3,/,0,S,3,/,0,0,1,编码后的状态表,/,F,x,0 0,0 1,1 1,1 0,Q,n+,1,2,Q,n+,1,1,Q,n,Q,n,2,1,01,/,0,00,/,0,00,/,0,00,/,0,00,/,0,11,/,0,10,/,0,10,/,0,15.5 时序逻辑电路的设计 例15-2 设计一个串行数据,25,15.5,时序逻辑电路的设计,例,15-2,选定触发器类型,Q,n,Q,n,2,1,Q,n+,1,1,Q,n+

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025开年第一课知敬畏守底线为2025年开门红营造风清气正的干事环境

- 高考倒计时100天学生与家长如何携手前行主题班会

- 2025民营企业座谈会要点速览促进民营经济发展

- 3月5日学习雷锋主题班会争做当代雷锋

- 三八妇女节致敬新时代的巾帼英雄

- 从井冈山歌谣感悟井冈山精神身体力行重唱红歌

- 三八妇女节致敬新时代的巾帼英雄

- 心理开学第一课家长应如何帮助孩子应对开学综合征

- 初三中考百日倒计时动员班会逆袭狂飙促奇迹

- 民俗文化二月二龙抬头主题班会二月二龙抬头风调雨顺好年头

- 3月5日学雷锋纪念日主题班会助人为乐无私奉献

- 幼儿园开学第一课家长会家园共育缓解入学焦虑

- 我们开学啦主题班会新学期新气象新起点

- 人教版四年级数学上册《笔算除法》教学课件

- 深入学习2025新修订《中小学生学籍管理办法》新办法新在哪里