CMOS芯片N阱剖面图

CMOS芯片N阱剖面图

《CMOS芯片N阱剖面图》由会员分享,可在线阅读,更多相关《CMOS芯片N阱剖面图(9页珍藏版)》请在装配图网上搜索。

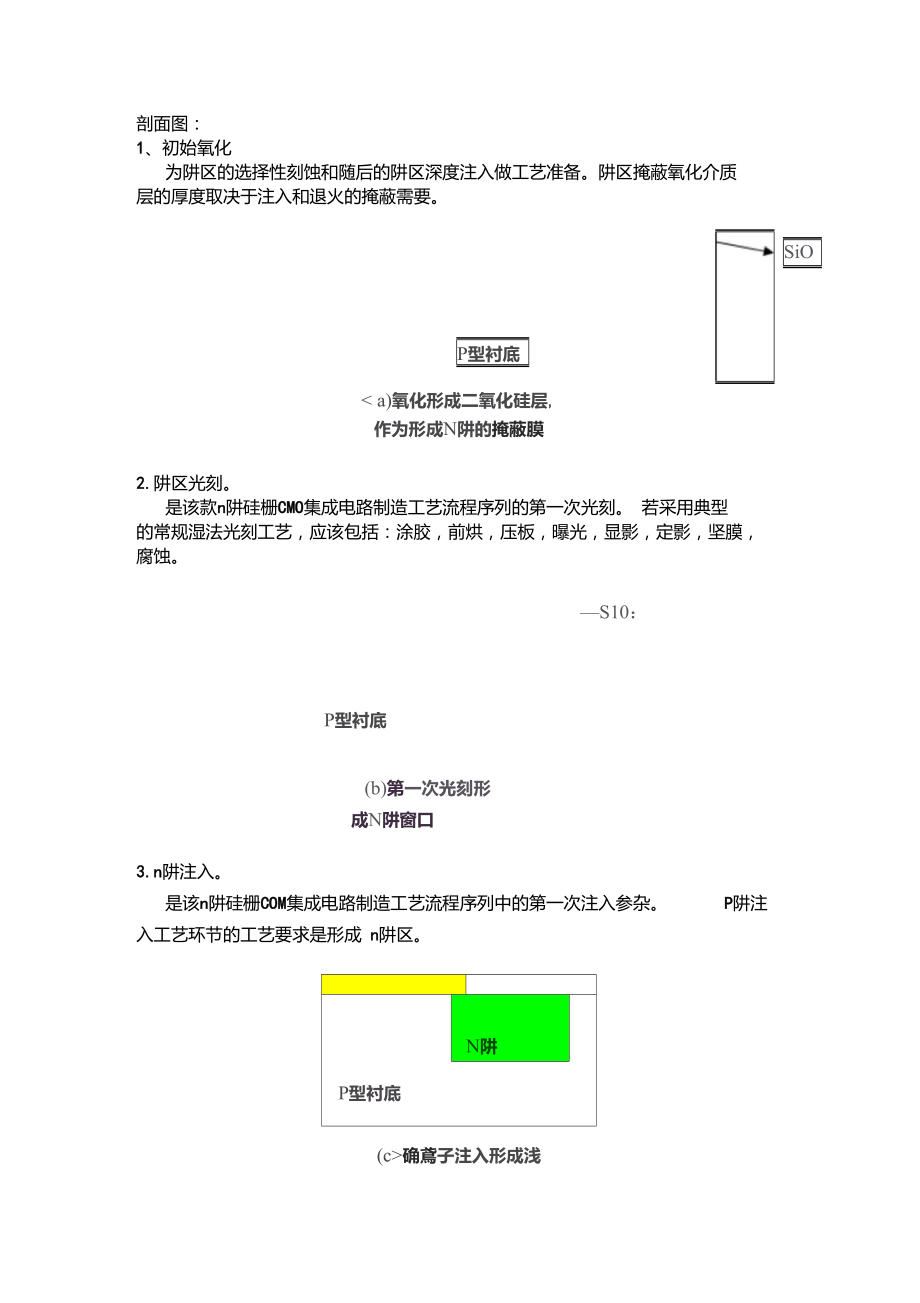

1、剖面图: 1、初始氧化 为阱区的选择性刻蚀和随后的阱区深度注入做工艺准备。阱区掩蔽氧化介质 层的厚度取决于注入和退火的掩蔽需要。 P型衬底 SiO: < a)氧化形成二氧化硅层, 作为形成N阱的掩蔽膜 2.阱区光刻。 是该款n阱硅栅CMO集成电路制造工艺流程序列的第一次光刻。 若采用典型 的常规湿法光刻工艺,应该包括:涂胶,前烘,压板,曝光,显影,定影,坚膜, 腐蚀。 —S10: P型衬底 (b)第一次光刻形 成N阱窗口 3.n阱注入。 是该n阱硅栅COM集成电路制造工艺流程序列中的第一次注入参杂。 P阱注 入工艺环节的工艺要求是形成 n阱区。

2、N阱

P型衬底

(c>确鳶子注入形成浅

结后,退火扩散形成N阱

4.剥离阱区氧化层

N阱

P型衬底

〔d)除去二氧化硅层

5.热生长二氧化硅缓冲层:

消除Si-Si3N4界面间的应力,第二次氧化

垫氧化层

N阱

P型衬底

(e)氧化形成垫氧

化层〉作为缓冲层

6.LPCVD制备 Si3N4 介质。

氮化硅层

< f) lpcvd形成氮化硅层

7.有源区光刻:即第二次光刻

P型衬底

3、化层

Npfl

P型衬底

Ch)用湿氧法生成二氧化 硅层用于器件隔离

9.剥离Si3N4层及SiO2缓冲层。

(1)刻蚀氮化硅 和垫氧化层

10.热氧化生长栅氧化层: 第四次氧化。

栅氧化层

第四次氧化形成栅氧 化层

11.生长多晶硅

多晶硅

4、

(好淀积多晶硅

12. 刻蚀多晶硅栅:

形成N沟MOS管和P沟MOS管的多晶硅栅欧姆接触层及电路中所需要的多晶 硅电阻区。

<0刻蚀多晶硅形成源

漏区掺杂窗口

13. 涂覆光刻胶,刻蚀n沟MOS管区域的胶膜,形成CMO管的源区和漏区

宫子注入形成源漏区

光刻胶

14. 涂覆光刻胶,刻蚀p沟MOS管区域的胶膜,形成CMOS?的源区和漏区

N阱

(n)光刻胶掩膜保护nMOS源 漏区,硼离子注入形咸EMOSJS 漏区

15.去光刻胶

N阱

P型衬底

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。