IP101GR原理图

IP101GR原理图

《IP101GR原理图》由会员分享,可在线阅读,更多相关《IP101GR原理图(5页珍藏版)》请在装配图网上搜索。

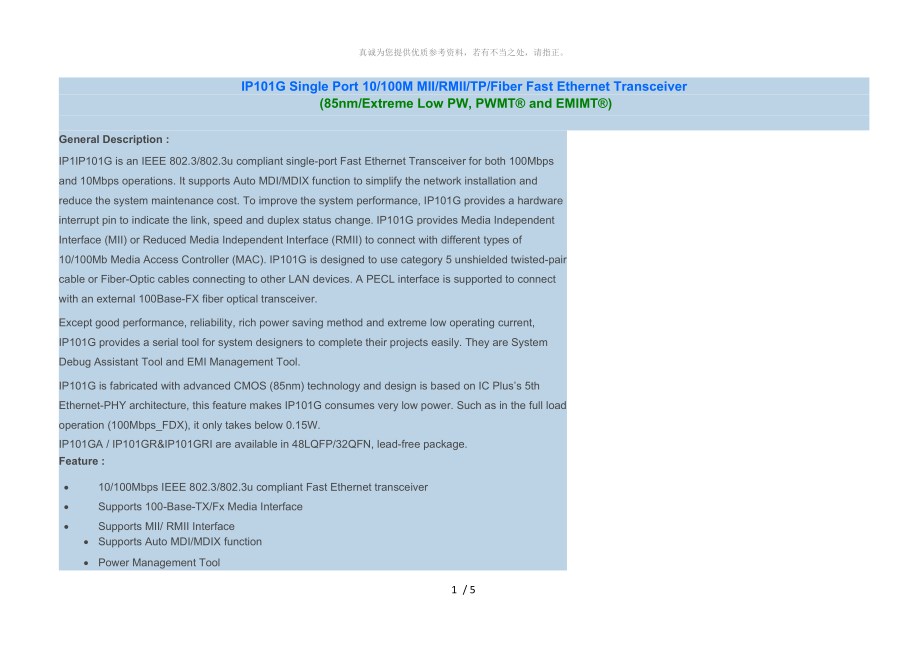

1、真诚为您提供优质参考资料,若有不当之处,请指正。 IP101G Single Port 10/100M MII/RMII/TP/Fiber Fast Ethernet Transceiver (85nm/Extreme Low PW, PWMT® and EMIMT®) General Description : IP1IP101G is an IEEE 802.3/802.3u compliant single-port Fast Ethernet Transceiver for both 100Mbps and 10Mbps operations. It supports

2、 Auto MDI/MDIX function to simplify the network installation and reduce the system maintenance cost. To improve the system performance, IP101G provides a hardware interrupt pin to indicate the link, speed and duplex status change. IP101G provides Media Independent Interface (MII) or Reduced Media In

3、dependent Interface (RMII) to connect with different types of 10/100Mb Media Access Controller (MAC). IP101G is designed to use category 5 unshielded twisted-pair cable or Fiber-Optic cables connecting to other LAN devices. A PECL interface is supported to connect with an external 100Base-FX fiber o

4、ptical transceiver. Except good performance, reliability, rich power saving method and extreme low operating current, IP101G provides a serial tool for system designers to complete their projects easily. They are System Debug Assistant Tool and EMI Management Tool. IP101G is fabricated with advanc

5、ed CMOS (85nm) technology and design is based on IC Plus’s 5th Ethernet-PHY architecture, this feature makes IP101G consumes very low power. Such as in the full load operation (100Mbps_FDX), it only takes below 0.15W. IP101GA / IP101GR&IP101GRI are available in 48LQFP/32QFN, lead-free package. Fea

6、ture : · 10/100Mbps IEEE 802.3/802.3u compliant Fast Ethernet transceiver · Supports 100-Base-TX/Fx Media Interface · Supports MII/ RMII Interface · Supports Auto MDI/MDIX function · Power Management Tool - APS, auto power saving while Link-off - 802.3az, protocol based power saving - WOL

7、+, light traffic power saving - PWD, force-off power saving · Supports Base Line Wander compensation · Supports Interrupt function · Supports MDC and MDIO to communicate with the MAC · EMI Management Tool - F/W based control - 4 levels for mapping the difference layout length on the PCB · S

8、ingle 3.3V power supply · Built-in Vcore regulator · DSP-based PHY Transceiver technology · System Debug Assistant Tool - 16 bit RX counter - 9 bit RXER/CRC counter - Isolate MII/RMII - RX to TX Loopback - Loopback MII/RMII · Using either 25MHz crystal/oscillator or 50MHz oscillator REF_C

9、LK as clock source · Built-in 49.9ohm resistors for simplifying BOM · Flexible LED display · Process: 85nm · Package and operation temperature - IP101G: dice, 0~70 - IP101GA: 48LQFP, 0~70 - IP101GR: 32QFN, 0~70 - IP101GRI: 32QFN, -40~85 Feature : · NAS · Network Printers and Servers · IP Set-Top Box · IP/Smart TV · Game console · IP and Video Phone · PoE · Telecom Fiber device 5 / 5

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。